# Solutions - Homework 3

(Due date: March 18th @ 11:59 pm)

Presentation and clarity are very important! Show your procedure!

### PROBLEM 1 (11 PTS)

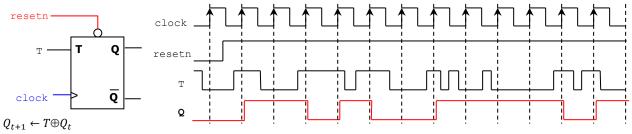

a) Complete the timing diagram of the circuit shown below. (5 pts)

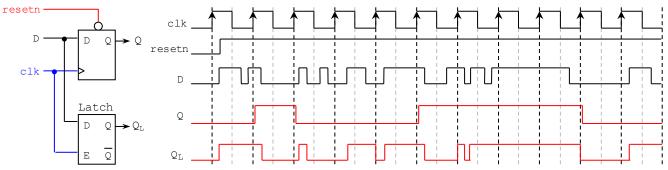

b) Complete the timing diagram of the circuits shown below: (6 pts)

### PROBLEM 2 (17 PTS)

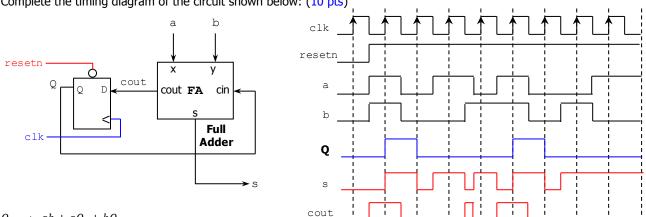

Complete the timing diagram of the circuit shown below: (10 pts) .

$Q_{t+1} \leftarrow ab + aQ_t + bQ_t$

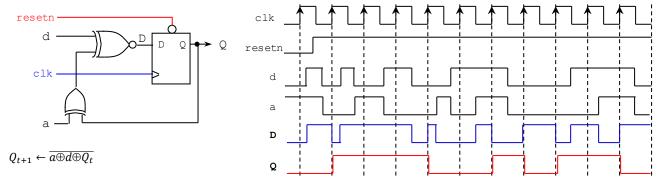

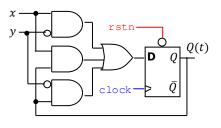

Complete the timing diagram of the circuit shown below. Get the excitation equation for Q. (7 pts)

### PROBLEM 3 (10 PTS)

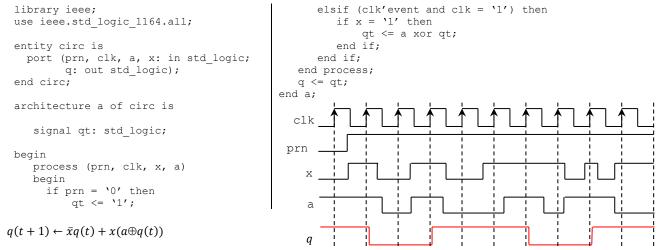

a) Complete the timing diagram of the circuit whose VHDL description is shown below. Also, get the excitation equation for q.

b) With a flip flop and logic gates, sketch the circuit whose excitation equations is given by (4 pts):  $Q(t + 1) \leftarrow x\overline{y} + xQ(t) + \overline{y}Q(t)$

### PROBLEM 4 (10 PTS)

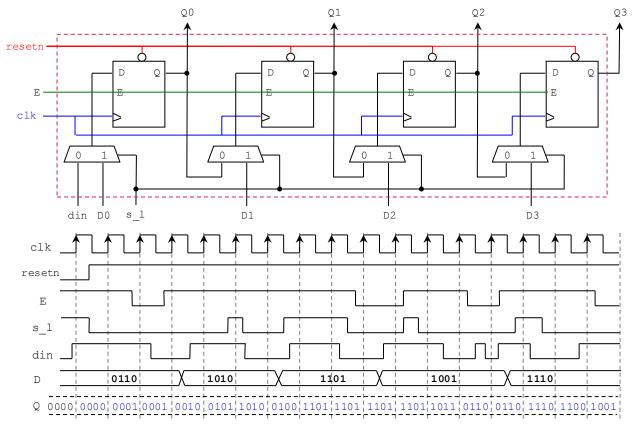

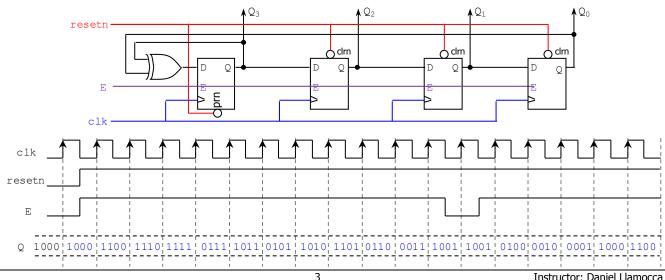

Complete the timing diagram of the following 4-bit parallel access shift register with enable input.

When E=1: If s\_1=0 (shifting operation). If s\_1=1 (parallel load) Note that Q = Q<sub>3</sub>Q<sub>2</sub>Q<sub>1</sub>Q<sub>0</sub>. D = D<sub>3</sub>D<sub>2</sub>D<sub>1</sub>D<sub>0</sub>

### PROBLEM 5 (12 PTS)

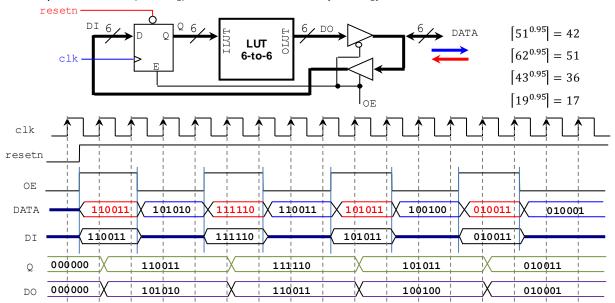

Given the following circuit, complete the timing diagram (signals *DO*, *O*, and *DATA*). The LUT 6-to-6 implements the following function:  $OLUT = [ILUT^{0.95}]$ , where ILUT is an unsigned number. For example:  $ILUT = 54 (110110_2) \rightarrow OLUT = [54^{0.95}] = 45 (101101_2)$

### PROBLEM 6 (22 PTS)

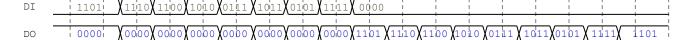

a) For the following circuit, complete the timing diagram and get the excitation equations of the flip flop outputs.  $Q = Q_3 Q_2 Q_1 Q_0$ .  $Q_3(t+1) \leftarrow \overline{E}Q_3(t) + E(Q_3(t) \oplus Q_0(t))$

$Q_2(t+1) \leftarrow \overline{E}Q_2(t) + EQ_3(t)$  $Q_1(t+1) \leftarrow \overline{E}Q_1(t) + EQ_2(t)$  $Q_0(t+1) \leftarrow \overline{E}Q_0(t) + EQ_1(t)$

- b) Write the VHDL for the given circuit and simulate your circuit.

- ✓ Write structural VHDL code. Create two files: i) flip flop, ii) top file (where you will interconnect the flip flops and the logic gates). (10 pts)

- reset input: It is connected to the preset input of flip flop  $Q_3$ , and to the reset input of flip flops  $Q_2$ ,  $Q_1$ ,  $Q_0$ .

- ✓ Write a VHDL testbench according to the timing diagram shown below. Run the simulation (Behavioral Simulation) and verify the results by comparing them with the simulation you completed manually. The clock frequency must be 100 MHz with 50% duty cycle. (8 pts)

- c) Upload (as a .zip file) the following files to Moodle (an assignment will be created):

- ✓ VHDL code files and testbench.

- $\checkmark$  A screenshot of your Vivado simulation results (it should show the values for Q).

#### ✓ VHDL Code: Top File

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity lfsr_prbsg is

generic (N: INTEGER:= 4);

port ( resetn, clock: in std logic;

E: in std logic;

Q: out std logic vector (N-1 downto 0));

end lfsr prbsg;

architecture structural of lfsr prbsg is

component dffe

port ( d : in STD LOGIC;

clrn: in std logic:= '1';

prn: in std logic:= '1';

clk : in STD_LOGIC;

ena: in std logic;

q : out STD LOGIC);

end component;

signal D, Qt: std logic vector (N-1 downto 0);

begin

D(N-1) \le Qt(N-1) \text{ xor } Qt(0);

g0: for i in N-2 downto 0 generate

D(i) <= Qt(i+1);

end generate;

df: dffe port map (d => D(N-1), clrn => '1', prn => resetn, clk => clock, ena => E, q => Qt(N-1));

g1: for i in N-2 downto 0 generate

di: dffe port map (d => D(i), clrn => resetn, prn => '1', clk => clock, ena => E, q => Qt(i));

end generate;

Q <= Qt;

```

end structural;

#### ✓ VHDL Code: D-Type flip flop

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.STD LOGIC UNSIGNED.ALL;

entity dffe is

port ( d : in STD LOGIC;

clrn, prn, clk, ena: in std logic;

q : out STD LOGIC);

end dffe;

architecture behaviour of dffe is

begin

process (clk, ena, prn, clrn)

begin

if clrn = '0' then q <= '0';

elsif prn = '0' then q <= '1';

elsif (clk'event and clk='1') then

if ena = '1' then q <= d; end if;

end if;

end process;

end behaviour;

```

#### ✓ VHDL Tesbench:

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_lfsr_prbsg IS

generic (N: integer:= 4);

END tb lfsr prbsg;

```

## ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT, OAKLAND UNIVERSITY ECE-2700: Digital Logic Design

```

ARCHITECTURE behavior OF tb lfsr prbsg IS

component lfsr prbsg

port ( resetn, clock: in std_logic;

E: in std logic;

Q: out std_logic_vector (N-1 downto 0));

end component;

-- Inputs

signal E : std logic := '0';

signal resetn : std_logic := '0';

signal clock : std_logic := '0';

-- Outputs

signal Q : std logic vector(N-1 downto 0);

-- Clock period definitions

constant T : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: lfsr prbsg PORT MAP (resetn => resetn, clock => clock, E => E, Q => Q);

-- Clock process definitions

clock_process :process

begin

clock <= '0'; wait for T/2;</pre>

clock <= '1'; wait for T/2;</pre>

end process;

-- Stimulus process

stim_proc: process

begin

E <= '0'; wait for 100 ns;</pre>

-- hold reset state for 100 ns.

resetn <= '1';</pre>

E <= '1'; wait for 11*T;</pre>

E <= '0'; wait for T;

E <= '1'; wait for 6*T;</pre>

E <= '0';

wait;

end process;

```

END;

| Value |             | 100 | ns   |       | 150 | ns  | 8 6 |      | 00 ns   |      |    | 50 n: | 5   | 10     | 300 | ns | 6   | 2 | 350 1 | is<br>I I |      | 400 | ) ns | 6 6  |

|-------|-------------|-----|------|-------|-----|-----|-----|------|---------|------|----|-------|-----|--------|-----|----|-----|---|-------|-----------|------|-----|------|------|

| 1     |             |     |      |       |     |     |     |      |         |      |    |       |     |        |     |    |     |   |       |           |      |     |      |      |

| 0     |             |     |      |       |     |     |     |      |         |      |    |       | 1.1 |        |     |    |     |   |       |           |      |     |      |      |

| 0     |             |     |      |       |     |     |     |      |         |      |    |       |     |        |     |    |     |   |       |           |      |     |      |      |

| 1110  | 100         | X   | 1100 | X1110 | 111 | 1/0 | 111 | 101. | 1 / 010 | 1/10 | 10 | 1101  | 011 | 0 / 00 | ΞX  | 1  | 001 |   | 0100  | X00       | 10/0 | 001 | 1000 | 1100 |

|       |             |     |      |       |     |     |     |      |         |      |    |       |     |        |     |    |     |   |       |           |      |     |      |      |

|       |             |     |      |       |     |     |     |      |         |      |    |       |     |        |     |    |     |   |       |           |      |     |      |      |

|       | 1<br>0<br>0 |     |      |       |     |     |     |      |         |      |    |       |     |        |     |    |     |   |       |           |      |     |      |      |

### **PROBLEM 7 (8 PTS)**

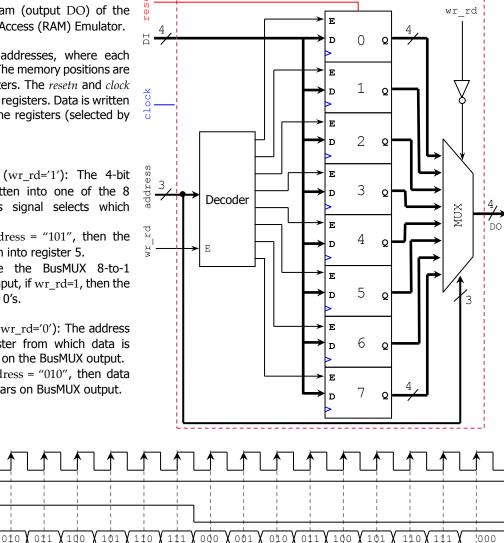

- Complete the timing diagram (output DO) of the following Random Memory Access (RAM) Emulator.

- RAM Emulator: It has 8 addresses, where each address holds a 4-bit data. The memory positions are implemented by 4-bit registers. The *resetn* and *clock* signals are shared by all the registers. Data is written or read onto/from one of the registers (selected by the signal address).

- **Operations:**

clock

resetn wr rd

address

- ✓ Writing onto memory (wr rd='1'): The 4-bit input data (DI) is written into one of the 8 registers. The address signal selects which register is to be written.

- For example: if address = "101", then the value of DI is written into register 5.

- Note that because the BusMUX 8-to-1 includes an enable input, if wr\_rd=1, then the BusMUX outputs are 0's.

- Reading from memory (wr\_rd='0'): The address  $\checkmark$ signal selects the register from which data is read. This data appears on the BusMUX output.

- For example: If address = "010", then data from register 2 appears on BusMUX output.

### PROBLEM 8 (10 PTS)

000

001

- Attach your Project Status Report (no more than 1 page, single-spaced, 2 columns, only one submission per group). This report should contain the initial status of your project. For formatting, use the provided template (Final Project - Report Template.docx). The sections included in the template are the ones required in your Final Report. At this stage, you are only required to:

- ✓ Include a (draft) project description and title.

- ✓ Include a draft Block Diagram of your hardware architecture.

- As a guideline, the figure shows a simple Block Diagram. There are input and output signals, as well as internal components along with their interconnection.

- ✓ At this stage, only a rough draft is required. There is no need to go into details: it is enough to show the tentative toplevel components that would constitute your system as well as the tentative inputs and outputs.

- Only student is needed to attach the report (make sure to indicate all the team members).